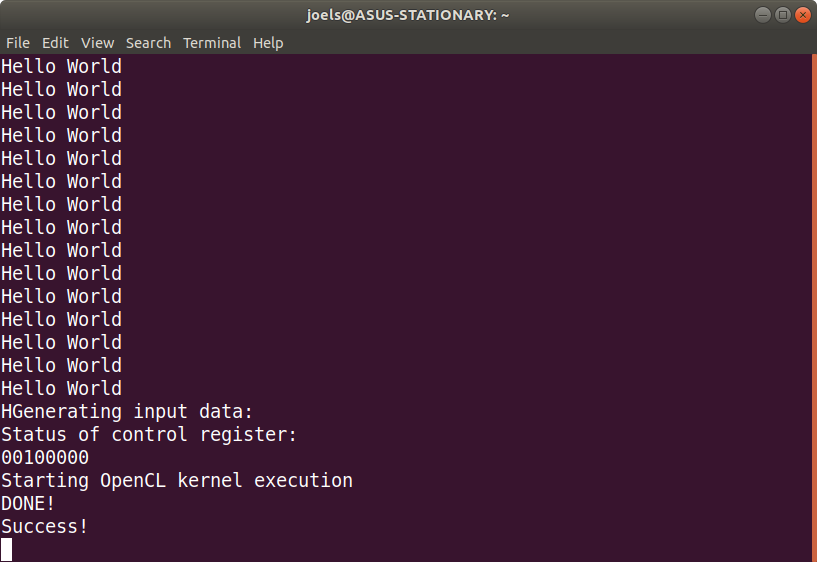

It seems your code has been initially written to run on a standard CPU, hence not every construct used in the code is suitable for FPGA acceleration. IntelFPGA/18.1/hld/board/terasic/de5net/tests/fft1Dint/device/ fft1dint.cl:1424: Compiler Warning: Aggressive compiler optimization: removing unnecessary storage to local memoryĮrror: exception "std::bad_alloc" in PostBuildSteps Error: Verilog generator FAILED.Ĭould you please provide me more information about this error? How can I understand which error in my code is linked to this output (buffer allocation or something else)? several warnings about auto unrolled loop.Ĭompiler Warning: removing out-of-bounds accesses to xtmp1.i.i.iĬompiler Warning: removing out-of-bounds accesses to xtmp2.i.i.iĬompiler Warning: removing out-of-bounds accesses to xtmp3.i.i.i aocx for the DE5-Net, the compiler returns with the following warnings and one error (after 5/6 hours of compilation): The OpenCL emulator gives me correct results when I run the code on the x86 machine. Thus, I am trying to compile my code, which is an integer iFFT based on the Cooley-Tukey algorithm.

I successfully run the examples provided by Intel FPGA for OpenCL and they work. I would like to use OpenCL SDK for a Terasic DE5-Net to deploy my algorithm (I am using Quartus 18.1 and OpenCL SDK 18.1).

0 Comments

Leave a Reply. |

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed